Viện nghiên cứu tại Thuỵ Sỹ của IBM – IBM Research Zurich – đang liên minh cùng Infineon Technologies AG, Global Foundries và nửa tá các học viện hoặc trung tâm nghiên cứu tại châu Âu trong một dự án có tên Steep, nhằm tìm ra một giải pháp để giảm thiểu mức điện năng tiêu thụ xuống gấp 10 lần và ở chế độ nghỉ xuống gần zero. Niềm tin của dự án này được đặt lên các transistor hiệu ứng trường hầm chui (T-FET).

Dự án Steep được tài trợ bởi chính phủ châu Âu là một nỗ lực để cải thiện những gì hiện có trên các T-FET, bằng cách dùng các kênh dây dẫn nano (nanowire), vật liệu silicon germanium và silicon III-V (III-V-on-silicon). Các cải thiện này về lý thuyết sẽ giảm đáng kể mức điện năng tiêu thụ trên T-FET. Và mục tiêu mà Steep đưa ra là có thể tạo ra một dây chuyền sản xuất T-FET có thể áp dụng trực tiếp được vào dây chuyền sản xuất CMOS hiện có, giúp quá trình chuyển đổi từ CMOS qua T-FET gặp ít rủi ro nhất. Dự án được đầu tư 5,5 triệu USD và kéo dài trong vòng 3 năm.

Trưởng nhóm nghiên cứu vật liệu dẫn điện nano tại IBM Research Zurich, Heike Riel, nói về các T-FET :

T-FET đã được biết đến từ 1994, nhưng chúng tôi muốn đem lại cho nó một cải thiện rõ rệt về hiệu năng

Mô hình (geometry) liên kết nano cho thấy một hiệu năng tĩnh điện tối ưu trên các cổng (gate) của chiếc FET. Và việc sử dụng các vật liệu bán dẫn mới như silicon III-V, cùng kỹ thuật strain lẫn điện môi trở cao (high-k) đương đại, sẽ giúp cải thiện năng lực của T-FET đồng thời giảm đáng kể mức điện áp cần thiết để hoạt động chiếc FET

Nhằm đạt hiệu năng cao trên T-FET với chỉ điện áp 0,5 V (CMOS thông thường cần đến 5V), các nghiên cứu viên của IBM lên kế hoạch dùng các liên kết nano dựa trên các vật liệu thuộc nhóm III-V như indium-arsenide. Khó khăn của việc này ở chỗ làm sao tạo ra được các liên kết trên một cách chính xác, vì phương pháp in litho có mặt nạ (mask lithography) không tạo ra các mắt lưới silicon III-V trùng khớp với ý định của nhà sản xuất.

Tuy vậy IBM đã dùng kỹ thuật tăng sinh epitaxy trên silicon III-V và đạt được những bước tiến nhất định với một diode hầm chui có tên Leo Esaki, người đã phát minh ra diode trên. Điểm đặc biệt của kỹ thuật mà IBM áp dụng là nó không cần đến các chất xúc tác (catalyst).

Chúng tôi dùng một phương pháp không cần xúc tác. Chúng tôi bắt đầu với một mặt nạ oxide nằm ở trên cùng lớp silicon, vốn đã đã được lên mẫu sẵn bằng các lỗ, rồi chúng tôi cho tăng sinh epitaxy trực tiếp các vật liệu nhóm III-V trên tấm silicon đó

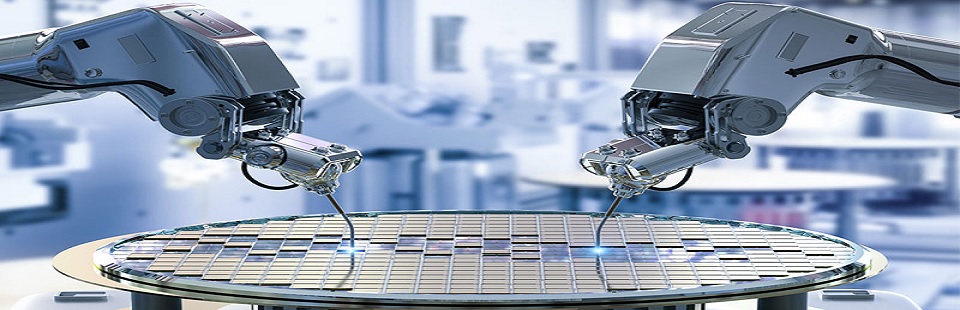

Các cột dọc sẽ tăng sinh thành một kênh dẫn transistor có đường kính chỉ vài nanometer trên tấm wafer silicon mà anh muốn làm ra các T-FET.

Theo EE Times