SystemC DataTypes

Saturday, 06 November 2021 20:56

Semicon Editor 01

Introduction

SystemC has large number of data types to support modelling of Hardware as well as modelling of fractional fixed-point. Since SytemC is based on C++, it supports all the data types of C++.

Last Updated ( Tuesday, 29 March 2022 00:44 )

Read more...

|

Introduction To SystemC Part II

Tuesday, 02 November 2021 15:40

Semicon Editor 01

Before We Start Before we jump into the details of SystemC language, lets looks at what SystemC offers for hardware modelling in brief.

Last Updated ( Tuesday, 29 March 2022 00:46 )

Read more...

Introduction To SystemC Part I

Tuesday, 02 November 2021 15:23

Semicon Editor 01

Introduction

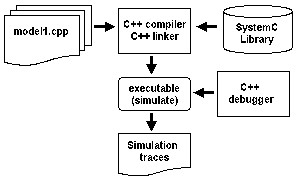

The SystemC Class Library has been developed to support system level design. It runs on both PC and UNIX platforms, and is freely downloadable from the web.

Last Updated ( Tuesday, 29 March 2022 00:46 )

Read more...

C++ Basics

Tuesday, 02 November 2021 13:30

Semicon Editor 01

Basics of C++. It is probably best to look at concrete examples of object oriented programming in C++ before going into further theory or concepts. We'll consider two kinds of examples.

Last Updated ( Tuesday, 29 March 2022 00:46 )

Read more...

Introduction To C++

Sunday, 31 October 2021 20:00

Semicon Editor 01

Introduction

C++ was developed by Bjarne Stroustrup of AT&T Bell Laboratories in the early 1980's, and is based on the C language. The name is a pun - "++" is a syntactic construct used in C (to increment a variable), and C++ is intended as an incremental improvement of C.

Last Updated ( Tuesday, 29 March 2022 00:46 )

Read more...

SystemC Modules Part III

Sunday, 31 October 2021 19:55

Semicon Editor 01

Module Instanciating

Instanciating modules in SystemC is same as in Verilog, same rules are followed. SystemC like Verilog allows two ways of connecting ports.

Last Updated ( Sunday, 12 June 2022 21:34 )

Read more...

SystemC Modules Part II

Sunday, 31 October 2021 19:31

Semicon Editor 01

Module Ports

Module Ports pass data to and from the processes of a module to the external world as in Verilog and VHDL. You declare a port direction as in, out, or inout. You also declare the data type of the port as any C++ data type,

Last Updated ( Tuesday, 29 March 2022 00:47 )

Read more...

SystemC Modules Part I

Saturday, 30 October 2021 13:58

Semicon Editor 01

Introduction

Modules are the basic building block within SystemC to partition a design. Modules allow designers to break complex systems into smaller more manageable pieces.

Last Updated ( Sunday, 12 June 2022 21:23 )

Read more...

Time In SystemC Part VI

Saturday, 30 October 2021 13:52

Semicon Editor 01

next_trigger()

next_trigger() is used with process methods, one's which are not threads. The function next_trigger does not suspend the method process instance; a method process cannot be suspended,

Last Updated ( Tuesday, 29 March 2022 00:48 )

Read more...

Time In SystemC Part V

Saturday, 30 October 2021 13:46

Semicon Editor 01

wait()

wait() suspends the thread or clocked thread process instance from which it is called for the very next occasion on which that process instance is resumed, and for that occasion only.

Last Updated ( Tuesday, 29 March 2022 00:48 )

Read more...

Time In SystemC Part IV

Thursday, 28 October 2021 13:54

Semicon Editor 01

sc_event sc_event is same as event in Verilog. It is used for process synchronization. A process instance may be triggered or resumed on the occurrence of an event, that is, when the event is notified.

Last Updated ( Tuesday, 29 March 2022 00:48 )

Read more...

Time In SystemC Part III

Thursday, 28 October 2021 13:42

Semicon Editor 01

sc_time_stamp () The function sc_time_stamp return's the current simulation time. During elaboration and initialization the function will return a value of zero.

Last Updated ( Tuesday, 29 March 2022 00:48 )

Read more...

Time In SystemC Part II

Tuesday, 26 October 2021 22:13

Semicon Editor 01

sc_start sc_start() is a key method in SystemC. This method starts the simulation phase, which consists of initialization and execution. sc_start() methods performs operations listed below.

Last Updated ( Tuesday, 29 March 2022 00:48 )

Read more...

Time In SystemC Part I

Tuesday, 26 October 2021 22:09

Semicon Editor 01

Introduction

Difference between a HDL and other programming language is notion of time and concurrancy. In this chapter we will see the time data type in detail.

Last Updated ( Tuesday, 29 March 2022 00:47 )

Read more...

Ports And Signals Part VI

Tuesday, 26 October 2021 14:13

Semicon Editor 01

Clocks Clocks are special objects in SystemC. They are used for generating clocks, that are used for synchronizing the events in SystemC models link in any other HDL.

Last Updated ( Tuesday, 29 March 2022 00:49 )

Read more...

Ports And Signals Part V

Sunday, 24 October 2021 20:42

Semicon Editor 01

Signal Binding Each port should be bound to a single signal. When reading a ports, the variable assigned to the port must have the same type as the port type.

Last Updated ( Tuesday, 29 March 2022 00:49 )

Read more...

|

|

|

|

|

|

|

Page 9 of 118 |