CÁC MÔ HÌNH TRONG VERILOG

CÁC MÔ HÌNH TRONG VERILOG

1. MÔ HÌNH MỨC CỔNG TRONG VERILOG

Mô hình mức cổng này thường sử dụng trong các thiết kế nhỏ, dễ tổng hợp nhất mô hình trong Verilog, và đúng với thiết kế lúc đầu chúng ta đặt ra.

Các cổng cơ bản Các từ khóa cơ bản của các cổng: and, nand, or, nor, xor, xnor

Các từ khóa cơ bản của các cổng: and, nand, or, nor, xor, xnor

Cú pháp:

<Tên cổng> <Tên_Custom>(Ngõ_ra, Ngõ_vào1, Ngõ_vào2…,Ngõ_vàon);

Ví dụ:

- and congand(y,a,b,c);

Sau câu lệnh này chúng ta sẽ có 1 cổng and có 3 ngõ vào là a, b, c và 1 ngõ ra đó là y. Tương tự cho các cổng còn lại. Chức năng và bảng trạng thái các bạn có thể tham khảo: Các cổng cơ bản trong kỹ thuật số

Khi mình sử dụng lệnh này thì chương trình sẽ tự gọi các cell có sẵn mà chương trình cung cấp.

Các cổng buf, not Từ khóa: buf, not

Từ khóa: buf, not

Cú pháp:

<Tên cổng> <Tên_custom>(Ngõ_ra1, Ngõ_ra2,…,Ngõ_ran,Ngõ_vào)

Lưu ý: 2 cổng này có thể có nhiều ngõ ra những chỉ có duy nhất một ngõ vào

Ví dụ:

- not not1(x,y,z,a);

Tạo ra một cổng not đảo ngược giá trị của a và gán giá trị đó cho tất cả các ngõ ra x, y, z

Cổng buf là một cổng đệm. giúp nâng điện áp để tránh suy giảm trên đường truyền tín hiệu.

Các cổng 3 trạng thái

Từ khóa: bufif1, bufif0, notif0, notif1

Các cổng này hoạt động như cổng buf, not nhưng có thêm một chân điều khiển tích cực mức 0 hoặc mức 1 tùy theo từ khóa mà mình chọn.

Cú pháp:

<Tên cổng> <Tên_thể_hiện>(Ngõ_ra,Ngõ vào,Chân_điều_khiển);

Thường thì mô hình mức cổng ít được sử dụng nhất của các mô hình trong Verilog. Nhưng các thiết kế cũng không thể thiếu đi mô hình này để tối ưu và gần hơn với thiết kế.

2. MÔ HÌNH LUỒNG DỮ LIỆU (DATAFOLOW)

Mô hình luồng dữ liệu mô tả thiết kế dưới dạng biểu thức thay vì thể hiện bằng các cổng cơ bản được dùng nhiều thứ 2 mô hình trong Verilog. Các biểu thức, toán hạng, toán tử là nền tảng căn bản của mô hình luồng dữ liệu vì vậy để học mô hình này các bạn cần đọc trước bài: Biểu thức, toán hạng, toán tử căn bản trong Verilog.

Câu lệnh cơ bản được dùng là assign, dùng để gán một giá trị hày biểu thức đến một biến kiểu net.

Phép gán thông thường: assign biến_kiểu_wire = Biến_or_biểu_thức;

Gán ẩn lúc khai báo: wire biến = Biến_or_biểu_thức;

Cũng có thể gán trực tiếp giá trị vào biến.

Ví dụ:

- wire y;

- assign y = a & b;

- wire y = a & b ;

3. MÔ HÌNH HÀNH VI

Kiểu mô tả được sử dụng nhiều nhất và phổ biến nhất của các mô hình trong Verilog. Thường dùng trong các thiết kế lớn. Có lẽ cái kiểu mô hình hành vi này mình sẽ viết riêng vào một bài vì nó khá dài và khá quan trọng. Link mình sẽ chèn vào đây sớm nhất có thể.

Theo http://laptrinhvnc.com/

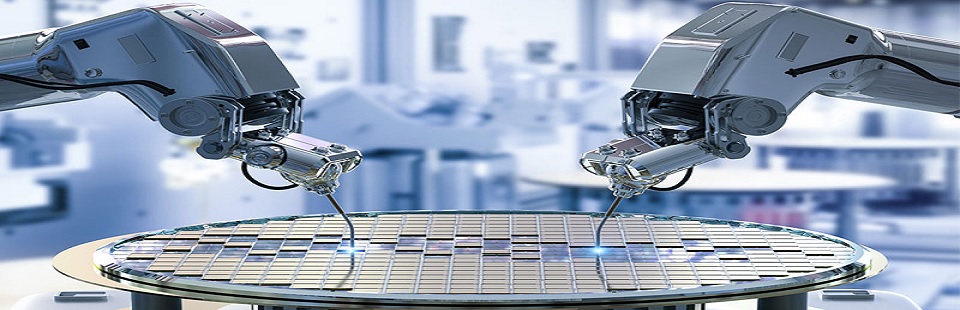

Bạn có đam mê ngành thiết kế vi mạch và bạn muốn có mức lương 1000 usd cùng lúc bạn

đang muốn tìm một Trung tâm để học vậy hãy đến với ngành vi mạch tại SEMICON

HotLine: 0972 800 931 or 0938 838 404 Ms Duyên