1. Thế nào là môi trường mô phỏng (simulation environment)

1. Thế nào là môi trường mô phỏng (simulation environment)

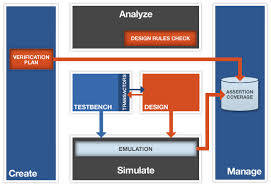

Trong thiết kế ASIC, môi trường mô phỏng được sử dụng để kiểm tra tính đúng đắn của thiết kế (thông thường là về mặt logic).

Môi trường mô phỏng bao gồm các thành phần: công cụ mô phỏng, thư viện, script thực thi, các dữ liệu input, output và DUT (design under test). Môi trường mô phỏng có thể được xây dựng để kiểm tra chức năng của tất cả các khối trong một IC, hoặc có thể được xây dựng để kiểm tra chức năng của từng khối riêng rẽ. Ứng với hai loại môi trường mô phỏng này, chúng ta có hai khái niệm cơ bản sau:

2. Môi trường Combine test (CT simulation environment):

Dùng để kiểm tra tính đúng đắn của một khối (module), và của cả hệ thống khi khối này được tích hợp vào hệ thống. Thông qua việc kiểm tra này, người kiểm tra có thể phát hiện ra lỗi không chỉ của block do mình thiết kế mà còn kiểm tra được tính đúng đắn của các block khác, có liên kết với block của mình. Môi trường này thường được dùng chung bởi tất cả các thành viên trong đội thiết kế, để kiểm tra tính năng của block mình khi tích hợp vào hệ thống.

Nhược điểm của môi trường này là thời gian chạy lâu, do công cụ mô phỏng (simulator) phải đọc và compile (biên dịch) tất cả các thiết kế trong trong quá trình mô phỏng. Ngoài ra, việc kiểm tra bị giới hạn do việc điều khiển các dữ liệu vào và ra phải qua nhiều khối trung gian, gây khó khăn cho việc điều khiển và quan sát dữ liệu.

3. Môi trường Unit test (Unit test environment)

Dùng để kiểm tra tính đúng đắn của từng block riêng rẽ. Thông thường, môi trường này được xây dựng lên bởi người thiết kế block đó. Ưu điểm của môi trường này là chạy nhanh (số lượng thiết kế, dòng code nhỏ) và linh hoạt trong việc điều khiển các dữ liệu ngõ vào (input) để tạo ra các dữ liệu ngõ ra tương ứng (output). Do đó, người thiết kế có khả năng kiểm tra tính đúng đắn của từng dòng code mà mình thiết kế bằng cách điểu khiển các dữ liệu ngõ vào (stimulus) như mình mong muốn. Đồng thời có thể dễ dàng kiểm tra được độ bao phủ (coverge) của thiết kế có đạt được 100% hay không. Điều này gần như là không thể thực hiện được trong môi trường CT như đã nói ở trên.

Bạn có đam mê ngành thiết kế vi mạch và bạn muốn có mức lương 1000 usd cùng lúc bạn

đang muốn tìm một Trung tâm để học vậy hãy đến với ngành vi mạch tại SEMICON

HotLine: 0972 800 931 Ms Duyên