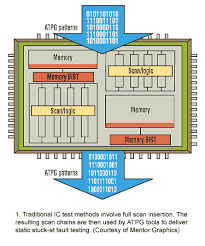

Trong quá trình thiết kế LSI, một trong những vấn đề luôn được quan tâm là làm thế nào để có thể kiểm tra được chất lượng của chip sau khi sản xuất (no defect). Design For Test (thiết kế để kiểm tra) mà semiconvn.com đã từng giới thiệu là một phương pháp như vậy.

hông qua việc thực hiện chèn các mạch test vào thiết kế logic, có thể đảm bảo được hơn 90% (~98%) logic của mạch sẽ được kiểm tra. Lưu ý ràng phương pháp này chỉ kiểm tra lỗi trong quá trình sản xuất, không kiểm tra được tính đúng đắn về mặt logic của mạch.

Một trong các phương pháp bỗ sung để nâng cao được chất lượng của LSI khi xuất xưởng, đảm bảo không lỗi là chạy thêm các pattern để kiểm tra về mặt chức năng và timing của LSI, đồng thời kiểm tra các mạch logic mà phương pháp Design For Test không thực hiện được (do không chèn được logic để kiểm tra).

Khác với DFT được làm một cách tự động bởi EDA tool, việc kiểm tra về bằng cách tạo thêm functional patternnày được làm hoàn toàn thủ công. Do đó, chất lượng của công đoạn này sẽ phụ thuộc rất nhiều vào việc các kĩ sư thiết kế hiểu được những thành phần nào cần phải được kiểm tra, ngoài DFT. Thông qua việc đánh giá các mạch logic không có khả năng cover bởi phương pháp DFT, các pattern sẽ được tạo ra nhằm test những logic này.

Học chi tiết hơn về chủ đề này tại semiconvn.com