Bài giới thiệu về clock gating. Một trong những kĩ thuật được áp dụng nhằm giảm mức tiêu hao năng lượng của mạch.

Bài giới thiệu về clock gating. Một trong những kĩ thuật được áp dụng nhằm giảm mức tiêu hao năng lượng của mạch.

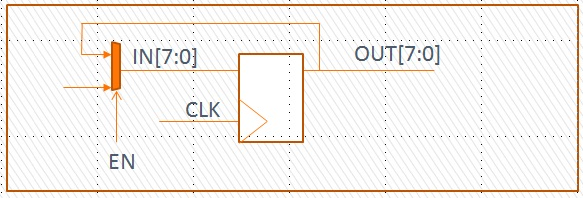

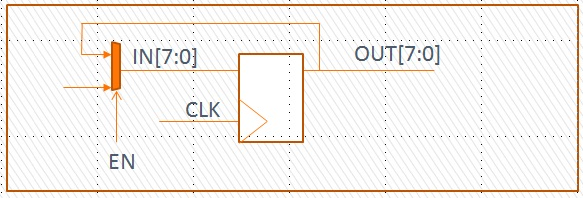

Xem xét hình ảnh sau về hoạt động của một FF với 8-bit data.

Với mạch như hình vẽ trên, dữ liệu IN[7:0] luôn luôn được đưa vào OUT[7:0] bất chấp trạng thái của EN.

- Khi EN = 1 : giá trị mới sẽ được cập nhật vào OUT

- Khi EN = 0: giá trị của OUT sẽ được gán là chính nó

Điều này làm cho mạch tiêu nao nhiều năng lượng do FF sẽ hoạt động liên tục ứng với mỗi chu kỳ CLK

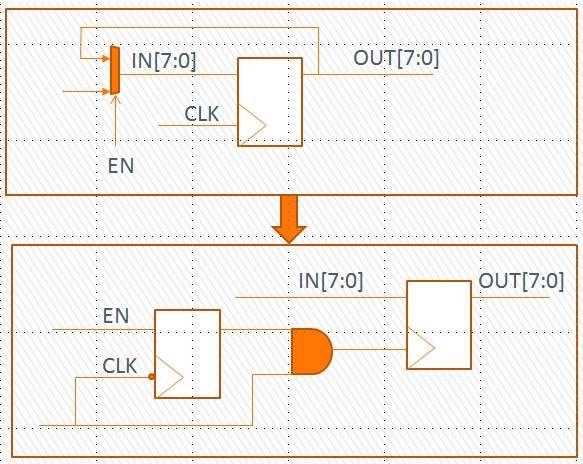

Xem xét mạch sau

Ở hình bên dưới, tín hiệu EN được dùng như một tín hiệu điều khiển clock của FF thứ hai. Khi và chỉ khi EN=1, FF thứ hai mới được cung cấp clock để hoạt động. Điều này làm cho tầng suất hoạt động của FF thứ hai sẽ ít đi so với hình ảnh đầu tiên, do vậy năng lượng tiêu thụ cũng sẽ giảm đi. Đây được gọi là clock gating.

Việc chèn gating cell sẽ được làm một cách tự động trong quá trình tổng hợp (synthesize), các kĩ sư thiết kế sẽ không trực tiếp can thiệp vào quá trình này. Tuy nhiên việc chèn thêm mạch gating sẽ làm tăng gate size của mạch, do vậy phương pháp này sẽ được áp dụng tốt hơn đối với một nhóm FF có chung tín hiệu EN.

Thiết Kế Vi Mạch, Thiết Kế IC là gì? Tại sao nên học vi mạch? Vì mức lương trên 1000 USD trong 2 năm! bạn có muốn đạt được.

Semicon đã mang đến sự hài lòng và những thành công lớn trong tương lai cho các học viên.

ª CHÚNG TÔI SEMICON SẼ GIÚP BẠN TIẾP CẬN CÁC DOANH NGHIỆP NHANH NHẤT"

Hãy đăng ký khóa học ngay và gửi hồ sơ xin việc các bạn đến Semiconª

Video giới thiệu SEMICON IC DESIGN TRAINING CENTER