Tìm hiều về kiến trúc clock của hệ thống System On Chip (SoC)

Tìm hiều về kiến trúc clock của hệ thống System On Chip (SoC)

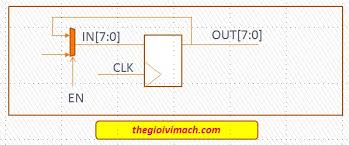

Một trong những kiến trúc clock thông dụng trong một hệ thống SoC được mô tả như hình dưới đây.

reference_clock: thông thường là các clock có tầng số thấp (khoảng vài chục Mhz) được tạo ra từ thạch anh.

Phase Lock Loop (PLL): Bộ nhân tần số clock (analog design). Các PLL ngày này có thể nhân tần số clock lên từ vài chục đến hàng trăm lần tầng số reference_clock ban đâu.

Mutiplier: Bộ chia clock để tạo ra các tần số nhỏ hơn, đáp ứng yêu cầu sử dụng của các thành phần trong hệ thống.

MUX: Bộ chọn clock, dùng để chọn clock có tầng số mong muốn và đưa đến các module (block) cụ thể trong hệ thống. Các tín hiệu control có thể điều khiển được bằng SW, qua đó tầng số của một số module có thể thay đổi được trong quá trình hoạt động.

Thiết Kế Vi Mạch, Thiết Kế IC là gì? Tại sao nên học vi mạch? Vì mức lương trên 1000 USD trong 2 năm! bạn có muốn đạt được.

Semicon đã mang đến sự hài lòng và những thành công lớn trong tương lai cho các học viên.

ª CHÚNG TÔI SEMICON SẼ GIÚP BẠN TIẾP CẬN CÁC DOANH NGHIỆP NHANH NHẤT"

Hãy đăng ký khóa học ngay và gửi hồ sơ xin việc các bạn đến Semiconª

Video giới thiệu SEMICON IC DESIGN TRAINING CENTER