Thế nào là tổng hợp trong thiết kế ASIC.

Thế nào là tổng hợp trong thiết kế ASIC.

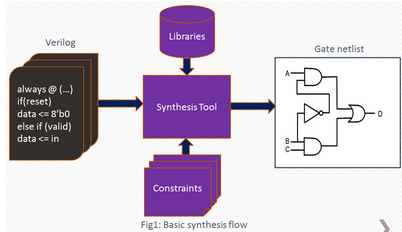

Synthesis (tổng hợp) là quá trình chuyển đổi từ dạng ngôn ngử mô tả ở mức cao thành dạng mức cổng

và xem xét các yếu tố về mặt tối ưu timing, diện tích, năng lượng tiêu thụ.Quá trình này được thực hiện bằng cách sử dụng công cụ của ví dụ như Design Compiler của Synopsys, Encounter RTL Compiler XL của Cadence. Quy trình tổng hợp được mô tả như hình dưới đây:

Trong quá trình tổng hợp các thư viện cell cơ bản (standard cell) ví dụ như các cổng AND, OR, NOT, các marco cell ví dụ như bộ cộng, bộ mux và các thành phần bộ nhớ (FF) được sử dụng. Do vậy, khi thiết kế Verilog, người thiết kế phải cân nhắc các yếu tố về mặt timing, diện tích, vấn đề tiêu thụ năng lượng của mạch trước quá trình tổng hợp. Từ đó, quá trình tổng hợp sẽ cho ra kết quả tốt.

Cách viết Verilog phù hợp với quá trình tổng hợp (synthesizable)

Một trong những điều cần lưu ý khi thiết kế Verilog là không phải tất cả các thiết kế ở mức RTL đều có thể áp dụng trong quá trình tổng hợp để tạo ra mức gate.

Ví dụ các từ khóa như initial, fork join, force and release, real sẽ không tổng hợp được bằng công cụ tổng hợp. Những từ khóa này chỉ được dùng trong quá trình mô phỏng để kiểm tra thiết kế.

Ngoài ra, có những thiết kế sẽ được tổng hợp được, tuy nhiên kết quả tổng hợp sẽ không như mong muốn do không tuân thủ quy tắc “thiết kế để tổng hợp”.

Quá trình tối ưu trong synthesis

Trong quá trình thiết kế, một trong những bài toán được đặt ra khi chúng ta còn đi học là làm sao để tối giản được thiết kế dựa vào các phép toán rút gọn. Tuy nhiên trong thực tế ngày này, việc tối giản thiết kế ở mức RTL là điều gần như không cần thiết (đặc biệt là khi viết các mạch tổ hợp – combination logic). Các công cụ thiết kế ngày nay đủ thông minh để thực hiện việc tối ưu hóa này một cách tốt nhất.