Công cụ mô phỏng (simulator)

Trong sơ đồ thiết kế ASIC, ứng với mỗi công đoạn thiết, các kỹ sư thiết kế sẽ dùng các công cụ mô phỏng tướng ứng.

Mục đích của công cụ mô phỏng là để kiểm tra tính đúng đắn của thiết kế để bảo đảm thiết kế sẽ không có lỗi trước khi chuyển qua một công đoạn khác, cũng như khi chế tạo ra sản phẩm.

Cùng với sự phát triển nhanh chóng của ngành công nghệ vi mạch, các nhà cung cấp cũng đưa ra những công cụ thiết kế với các tính năng vượt trội. Điều này không chỉ giúp cho công việc thiết kế được rút ngắn về mặt thời gian mà rủi ro có lỗi (bug) trong thiết kế cũng giảm xuống.

Các công ty lớn chuyển về cung cấp công cụ thiết kế có thể kể đến như Synopsys, Cadence, Mental Graphic, Aldec, Accelera, Atrenta. Trong đó hai nhà cung cấp cung cấp hàng đầu là Synopsys và Cadence, với các công cụ phục vụ cho hầu hết các giai đoạn trong quá trình thiết kế ASIC.

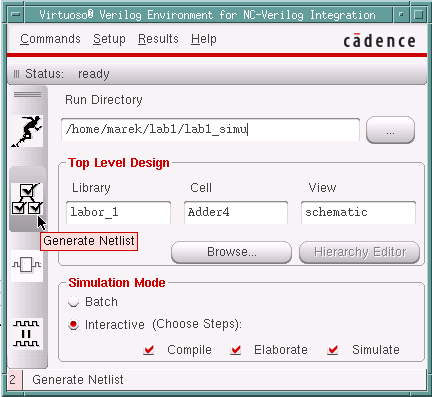

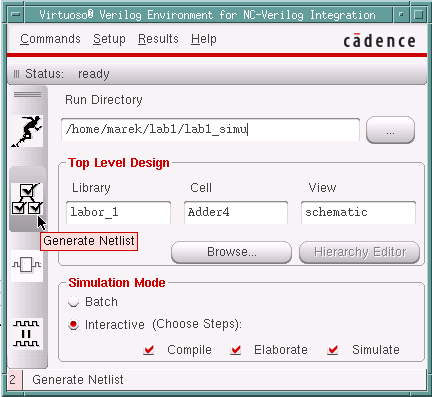

RTL (and gate) simulator: NCVerilog (Cadence), VCS (Synopsys), ModelSim (Mentor Graphics)

Đây là các công cụ được đánh giá là tốt nhất được sử dụng trong quá trình chạy mô phỏng để kiểm tra tích đúng đắn của thiết kế RTL. Trong đó, NC-Verilog được đánh giá cao hơn khi chạy mô phỏng ở mức Gate (cổng) nhờ thời gian chạy được rút ngắn hơn so với VCS.

Synthesis simulator (công cụ tổng hợp): Design Compiler (Synopsys), Encounter RTL Compiler XL (Cadence)

Đây là công cụ dũng để tổng hợp từ mức RTL sang mức Gate, với các tính năng vượt trội về việc tối ưu hóa thiết kế để đạt được những chỉ số tốt nhất về mặt timing, gate size (số lượng cổng nhỏ nhất), power consumption (năng lượng tiêu thụ ít nhất), …

Công cụ kiểm tra timing: Primetime (Synopsys)

Đây là công cụ phục vụ cho quá trình kiểm tra timing của thiết kế. Công cụ này có thể tính toán được timing của tất cả các đường (path) trong chip với các ràng buộc (constrainst) do kĩ sư thiết kế định nghĩa.

Công cụ kiểm tra tính ngang bằng về mặt logic: Encounter Conformal (Cadence), Formality (Synopsys)

Công cụ này phục vụ cho quá trình kiểm tra tính ngang bằng về mặt logic của hai thiết kế trong bất kỳ công đoạn nào của quá trình thiết kế ASIC. Ví dụ khi tổng hợp thiết kế từ mức RTL sang mức Gate, kỹ sư thiết kế sẽ dùng công cụ này kiểm tra để đảm bảo tính logic của thiết kế trước và sau khi tổng hợp là ngang bằng nhau. Encounter Conformal cung cấp các tính năng vượt trội so với Formality trong việc debug trong trường hợp hai thiết kế không bằng nhau. Từ đó sẽ xác định ra nguyên nhân lỗi và cách sửa lỗi một cách nhanh nhất.

Bạn Có Đam Mê Với Vi Mạch hay Nhúng - Bạn Muốn Trau Dồi Thêm Kĩ Năng

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn

Bạn Chưa Biết Phương Thức Nào Nhanh Chóng Để Đạt Được Chúng

Hãy Để Chúng Tôi Hỗ Trợ Cho Bạn. SEMICON

Hotline: 0972.800.931 - 0938.838.404 (Mr Long)