Vấn đề tiết kiệm năng lượng (low power consumption)

Vấn đề tiết kiệm năng lượng (low power consumption)

Vần đề tiết kiệm năng lượng ngày nay luôn được xem là một vấn đề lớn trong bất kì sản phẩm thiết bị cầm tay nào (handset).

Đó cũng là một trong những tiêu chí hàng đầu trong quyết định lựa chọn sản phẩm của khách hàng. Tuy nhiên, với công nghệ pin ở thời điểm hiện tại, các nhà sản xuất sản phẩm chỉ có thể tăng dung lượng pin bằng cách tăng kích cở của pin, đồng nghĩa với việc giá thành sẽ tăng theo.

Trong các sản phẩm này, SoC được xem là một trong những thành phần tiêu thụ năng lượng chính. Do vậy, tối ưu hóa được dòng năng lượng của chip đồng nghĩa với việc tăng thời lượng pin sử dụng của sản phẩm. Đây là một trong những vấn đề hàng đầu mà các nhà thiết kế ASIC (SoC) phải giải quyết.

Các phương pháp tiết kiệm năng lượng trong thiết kế ASIC

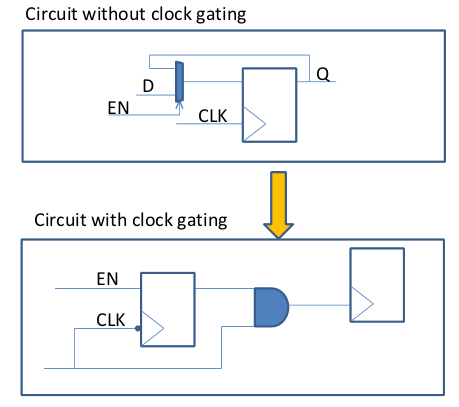

Cùng với sự hỗ trợ của các công cụ thiết kế, các phương pháp sau được dùng để giảm năng lượng tiêu thụ trong các mạch logic- Clock gating: Trong quá trình tổng hợp thiết kế (synthesis), các công cụ tổng hợp tối sẽ áp dụng phương pháp clock-gating để tất tín hiệu clock dựa vào trạng thái hoạt động của mạch. Khi nguồn clock bị tắt, mạch sẽ ở trạng thái tĩnh, không tiêu thụ năng lượng.

Hình bên dươí mô tả trạng thái mạch không áp dụng clock gating và mạch áp dụng clock gating (cổng AND). Ở hình phía trên, do CLK luôn dao động nên giá trị từ D sẽ chuyển qua Q ứng với mỗi chu kỳ của CLK, bất chấp giá trị của EN. Tuy nhiên, ở hình bên dưới cho thấy, chỉ khi nào giá trị của EN=1, thì mạch mới cấp xung clock cho FF phía sau hoạt động. Qua đó, lượng tiêu hao năng lượng của mạch dưới sẽ thấp hơn mạch bên trên.

- Sử dụng nhiều loại cell trong quá trình tổng hợp (Multi-Vth cells)

Trong quá trình tổng hợp, các công cụ tổng hợp sẽ sử dụng các loại cell khác nhau (khác nhau về kích cớ, độ tiêu hao năng lượng, tốc độ) cho các mạch khác nhau. Qua đó đảm bảo gate sau quá trình tổng hợp sẽ được tối ưu nhất, tùy vào độ ưu tiên:

Low Vth cell: Độ delay nhỏ, có thể sử dụng cho mạch hoạt động ở tẩng số cao, tuy nhiên mức hiêu hao năng lượng của cell này sẽ lớn

High Vth cell: Độ delay lớn, có thể sử dụng cho mạch hoạt động ở tầng số thấp, và mức năng lượng tiêu hao khi dùng loại cell này sẽ thấp.

- Cung cấp các nguồn khác nhau (Multi-voltage supply)

Đối với các block khác nhau cùng trong 1 chip, nguồn cung cấp có thể khác nhau tùy thuộc vào yêu cầu của hệ thống. Nguồn năng lượng thấp đồng nghĩa với việc lượng điện năng tiêu thụ thấp và ngược lại. Tuy nhiên, việc dùng nhiều nguồn năng lượng cấp vào sẽ gây nhiều khóa khăn trong quá trình thiết kế

- DVS, DVFS

DVS: Dynamic voltage scaling: Thay đổi voltage dựa theo yêu cầu về hiệu năng xử lý của hệ thống

DVFS:Dynamic voltage and frequency scaling:Thay đổi voltage và tầng số hoạt động theo yêu cầu của hệ thống.

- Power shut-off

Tắt nguồn của các block khi không ở trong trạng thái hoạt động

- Memory spliting

Tắt nguồn cung cấp của một số vùng nhớ khi không sử dụng

Lời kết

Vấn đề thiết kế tối ưu năng lượng tiêu thụ là vấn đề phức tạp, đòi hỏi người kĩ sư phải có nhiều kinh nghiệm trong lĩnh vực thiết kế vi mạch và hiểu được mô hình hoạt động của hệ thống. Việc kiểm tra tính đúng đắn của thiết kế này cũng đòi hỏi nhiều công sức do phải tạo ra nhiều bài test khác nhau.

Bạn có đam mê ngành thiết kế vi mạch và bạn muốn có mức lương1000 usd

hãy đến với ngành vi mạch tại SEMICON