Kiểu transistor nào sẽ thay thế finFET khi công nghệ bán dẫn chuyển sang thế hệ dưới 7nm? Cuộc tranh luận chỉ mới bắt đầu.

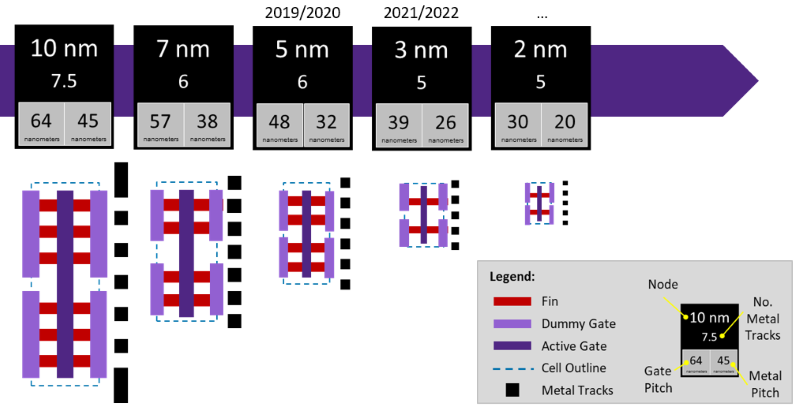

Các nhà sản xuất chíp đang lắp đặt thêm máy móc để sản xuất các chíp bán dẫn theo quy trình 16nm/14nm còn các công nghệ 10nm và 7nm thì cũng đang sắp sửa ra mắt.

Các công ty bán dẫn cũng đang nghiên cứu quy trình 5nm. TSMC hy vọng sẽ ra mắt công nghệ 5nm trước năm 2020. GlobalFoundries, Intel, và Samsung cũng có các hoạt động nghiên cứu và phát triển cho thế hệ công nghệ này.

Nhưng vẫn còn rất nhiều khó khăn và cả những điều chưa biết trong công nghệ 5nm. Trước hết, thời điểm và chi tiết kỹ thuật cụ thể của công nghệ 5nm vẫn còn mù mờ. Tiếp đến là hàng loạt trở ngại về mặt kĩ thuật và kinh tế. Và ngay cả khi công nghệ 5nm trở thành hiện thực, có lẽ cũng chỉ có vài công ty có đủ khả năng tài chính để dùng nó.

“Hiện tại tôi cho rằng 5nm sẽ thành hiện thực, nhưng sẽ không được đưa ra sản xuất đại trà trước năm 2020,” Bob Johnson, một nhà phân tích ở Gartner, chia sẻ. “Nếu phải dự đoán thì tôi cho rằng đó sẽ là năm 2021 hay 2022.”

“Một thiết kế SoC với độ phức tạp vừa phải trên công nghệ 5nm sẽ tốn 500 triệu đô-la hay hơn nữa,” Johnson nói. Để so sánh, Gartner cho biết chíp SoC 7nm sẽ tốn 271 triệu đô-la, gấp khoảng 9 lần so với công nghệ 28nm, là công nghệ dùng transistor dạng phẳng.

Với những công ty có khả năng chuyển sang thiết kế trên công nghệ 5nm thì có hai loại transistor chính đang cạnh tranh nhau cho công nghệ này—finFET và FET với cực cổng dạng vòng theo phương ngang (lateral gate-all-around FET). Gate-all-around (GAA), đôi khi còn được gọi là FET với kênh dẫn nanowire nằm ngang, là một finFET được lật ngang qua và có cực cổng vòng chung quanh.

Thực tế thì các công ty bán dẫn đang ủng hộ công nghệ gate-all-around. “Transistor GAA có các đặc tính tĩnh điện tốt hơn finFET, điều này có thể sẽ cho phép thu nhỏ chiều dài cực cổng thêm nữa,” theo Mark Bohr, một thành viên cao cấp và là giám đốc phụ trách kiến trúc và tích hợp quy trình công nghệ ở Intel.

Nhưng do khả năng hiện thực hoá gate-all-around vẫn còn bỏ ngõ nên công nghệ finFET cũng được xem xét cho mức 5nm. Cho dù sử dụng kiến trúc nào đi nữa thì khó khăn vẫn là phải làm sao cho công nghệ 5nm trở nên phổ biến hơn chứ không phải là chỉ được dùng trong một vài sản phẩm đặc biệt. Nếu không sẽ không đảm bảo được lợi nhuận. “Tôi cho rằng sẽ có một thế hệ công nghệ 5nm được dùng cho một số loại sản phẩm nào đó,” Bohr nói.

Hiện giờ, gate-all-around đang thu hút được nhiều sự chú ý nhất cho dù công nghệ này gặp nhiều khó khăn trong quá trình sản xuất. Việc chế tạo các chi tiết cấu trúc, các cực cổng, các nanowire, và các dây dẫn đều khó. Thêm vào đó, kiểm soát quy trình sản xuất cũng có thể cực kì khó khăn. Và, tất nhiên, khả năng chế tạo các transistor gate-all-around với chi phí thích hợp vẫn là điều then chốt.

Để giúp cho ngành công nghiệp bán dẫn hiểu thêm về transistor kiểu all-gate-around, Semiconductor Engineering sẽ giới thiệu quy trình sản xuất cơ bản và các thách thức đối với công nghệ này. Ngoài ra, bài viết còn có phần thảo luận về các linh kiện tương lai, như complementary FET và nanowire theo phương thẳng đứng.

Gate-all-around là gì?

Hiện nay, các công ty sản xuất chíp đang xây dựng cơ sở sản xuất finFET, nhưng không phải công ty nào cũng có công nghệ mới nhất này. Trong mạch logic, chẳng hạn, công nghệ tối ưu vẫn là 40nm và 28nm phẳng.

Nhiều nhà máy sản xuất chíp, thực tế, chỉ mới ”thấy có sự tăng trưởng trong công nghệ 28nm, đặc biệt là từ các khách hàng trong lĩnh vực thông tin,” theo như Po Wen Yen, giám đốc điều hành của United Microelectronics Corp. (UMC), cho biết trong một buổi nói chuyện mới đây. Chẳng hạn, tỷ lệ thời gian hoạt động của nhà máy 28nm của UMC trong quý 3 năm 2016 là 90%, so với mức khoảng 70% trong năm trước, Yen nói.

Thị trường cũng đang nóng dần lên đối với các công nghệ mới. Bắt đầu từ mức 22nm và 16nm/14nm, các nhà sản xuất chíp chuyển từ transistor dạng phẳng sang finFET. Lý do là vì finFET giúp vượt qua hiệu ứng kênh dẫn ngắn (short-channel effect) trong transistor dạng phẳng. Trong finFET, dòng điện được điều khiển thông qua một cực cổng bọc quanh ba mặt của một fin.

Nhưng đến một lúc nào đó thì finFET cũng sẽ gặp phải nhiều vấn đề. “Sau mức 7nm, chúng tôi thấy một số thách thức,” theo Kelvin Low, giám đốc tiếp thị cao cấp cho mảng dịch vụ sản xuất bán dẫn của Samsung. “Trước kia mỗi khi giảm khoảng cách CPP (contacted poly pitch) chúng tôi lại tăng được hiệu suất hoạt động của nguồn. Nhưng chúng tôi nghĩ rằng ở mức CPP bằng 7nm, điều này không còn đúng nữa. Phải có các cấu trúc khác và các kĩ thuật xử lý sức căng khác để giải quyết vấn đề này.”

Còn nữa, các kết nối bằng đồng—những sợi dây tí hon liên kết các transistor—càng lúc càng nhỏ hơn qua mỗi thế hệ công nghệ làm cho thời gian trễ do điện trở-điện dung (RC) trên chíp càng lúc càng tăng. ”Chúng tôi cho rằng độ trễ do hiệu ứng RC sẽ tăng lên đáng kể,” Low nói.

Nhìn chung, finFET có thể được tiếp tục phát triển để sử dụng cho công nghệ 5nm, mặc dù điều đó cần đến các vật liệu mới cho kênh dẫn. Một ý tưởng là thêm silicon germanium (SiGe) vào pMOS.

“Điều này giúp tăng hiệu năng mà không phải giảm chiều cao của fin,” theo Mike Chudzik, giám đốc cao cấp phụ trách chiến lược ở Applied Materials. “Thực ra, nó không cho phép bạn giảm chiều dài kênh dẫn. Nhưng nó làm tăng khả năng dẫn (mobility).”

Nhưng khi chiều dày của fin đạt đến mức khoảng 5nm thì finFET không còn khả năng phát triển nữa. “Ta có thể làm fin nhỏ hơn,” Chudzik nói. “Nhưng, đột nhiên, ta vấp phải hiệu ứng lượng tử (quantum confinement). Khoảng cách giữa các mức năng lượng (bandgap) tăng lên khi các fin trở nên quá mỏng. Và vì vậy điện áp ngưỡng tăng lên.”

Đó là lý do tại sao các công ty sản xuất chíp lại quan tâm đến gate-all-around. “(Gate-all-around) phức tạp hơn nhiều so với những gì chúng ta đang làm, nhưng đó là một bước phát triển tự nhiên từ finFET,” theo Dave Hemker, phó giám đốc cao cấp và giám đốc kĩ thuật ở Lam Research.

Mô tả ý tưởng transistor kiểu gate-all-arond cảu EPFL

Nhìn trên bề mặt thì gate-all-around giống như một MOSFET với cực gate nằm giữa cực drain và cực source. Thêm vào đó, gate-all-around lại chứa một finFET. Nhưng các fin không được chế tạo theo phương thẳng đứng như trong các finFET ngày nay mà được lật sang nằm ngang.

Transistor kiểu gate-all-around cũng chứa ba nanowire hay nhiều hơn. Các nanowire, tạo thành các kênh dẫn, được nối với cực source và cực drain. Kích thước của chúng thì rất đáng kinh ngạc. Chẳng hạn, IMEC mới đây trình diễn một transistor kiểu gate-all-around với các nanowire có đường kính 8nm.

Cực cổng bằng kim loại và ô-xit cách điện loại high-k, được dùng để điều khiển dòng điện, được đặt giữa cực source và cực drain. Câu hỏi được đặt ra vẫn là—Tại sao phải dùng gate-all-around? “Thực ra, tôi cho rằng nó không hẳn tốt hơn về mặt tĩnh điện,” Chudzik nói. “Ta muốn dùng gate-all-around do ta có thể thay đổi nó để cải thiện hiệu năng.”

Những người khác cũng đồng ý. “Không hẳn là khi chuyển từ finFET sang gate-all-around ta sẽ có được sự cải thiện đáng kể,” theo David Fried, giám đốc kĩ thuật của Coventor. “Ta chỉ có thêm được một chút khả năng điều khiển đặc tính tĩnh điện của transistor.”

Lợi ích lớn nhất, theo Fried, là khả năng giảm chiều dài kênh dẫn. “Kênh dẫn được bao bọc hoàn toàn và ta có khả năng điều khiển dòng điện tốt hơn,” ông nói. “Gate-all-around còn cho ta khả năng thu hẹp chiều dài kênh dẫn.”

Vậy loại transistor nào—finFET hay gate-all-around—tốt hơn cho công nghệ 5nm? Hiện tại thì điều này vẫn chưa thực sự rõ ràng do mỗi công nghệ có ưu và nhược điểm riêng.

Các công ty sản xuất chíp đang phải cân nhắc các quyết định khó khăn. “Sau hai hay ba thế hệ finFET nữa thì ta phải đối diện với câu hỏi thực sự đó là phải thay đổi vật liệu hay chuyển sang nanowire,” Hemker nói. “Transistor sẽ không đổi, nhưng (câu hỏi là) ta có thể đạt được tỷ lệ I_on/I_off với kích thước transistor mà ta muốn hay không?”

Ngoài ra, còn có các lựa chọn khác chẳng hạn như xếp chồng các con chíp theo kiểu 2.5D hay dùng các linh kiện 3D, và các công nghệ khác.

Chế tạo transistor kiểu gate-all-around

Có nhiều cách để tạo ra transistor kiểu gate-all-around. Trong một quy trình đơn giản, nhà sản xuất sẽ bắt đầu bằng việc chọn loại vật liệu cho cấu trúc pFET và nFET. Các lựa chọn cho pFET là silicon, germanium (Ge) hay SiGe. Cho nFET thì có thể dùng silicon, SiGe, Ge hay một loại vật liệu nhóm III-V.

Ge và III-V có khả năng dẫn cao hơn silicon, nhưng những vật liệu đặc biệt này dễ bị lỗi trong cấu trúc (defect) và có vấn đề về độ tin cậy (reliability). Do vậy, có lẽ cách đơn giản hơn là dùng silicon và/hoặc SiGe. “SiGe là một vật liệu dễ dùng hơn so với germanium và III-V,” theo Dan Mocuta, giám đốc về tích hợp và linh kiện logic ở Imec.

Ví dụ cụ thể: Quy trình chế tạo gate-all-around của Imec bắt đầu bằng cách hình thành một cấu trúc siêu lớp (super-lattice) bên trên tấm nền CMOS thông thường. Cấu trúc siêu lớp hình vuông của Imec có các lớp silicon và SiGe xen kẽ. Lý tưởng thì nó sẽ có ba lớp SiGe và ba lớp silicon.

Chế tạo một finFET (phẳng)

Sau khi có siêu lớp thì finFET mới được hình thành. Trong gate-all-around, fin được lật sang nằm ngang. Tuy vậy, các bước chế tạo vẫn giống như cách chế tạo finFET thông thường. Sử dụng các kĩ thuật thêm vật liệu (doping) thông thường từ một máy bắn ion (ion implanter), cực source và drain được hình thành bên trên cấu trúc siêu lớp, cực source ở một đầu còn cực drain ở đầu bên kia.

Sau đó, bề mặt bên trên của siêu lớp được tạo thành dạng hình chữ “H” bằng nhiều bước khắc quang học. Cấu trúc hình chữ H này nằm ngang.

Hai vạch đứng của chữ H là cực source và cực drain. Còn vạch ngang ở giữa là một phần của fin.

Quy trình này gặp một số trở ngại. Trong bước khắc quang học, hiện nay có hai công nghệ được dùng—khắc bằng tia cực tím (extreme ultraviolet, EUV) và khắc bằng ánh sáng bước sóng 193nm chiếu lên wafer đặt chìm trong nước (193nm immersion). Ở mức 5nm thì cho dù sử dụng công nghệ nào đi nữa ta cũng phải khắc nhiều lần.

Các nhà sản xuất chíp có thể dùng cả hai cách trên công nghệ 5nm. Mặc dù vậy, họ muốn dùng EUV cho mức 7nm và/hoặc 5nm để đơn giản hoá các bước khắc trong quy trình. “Nếu không có EUV thì số lớp mặt nạ sẽ tăng lên đáng kể,” Low nói. “Với EUV, chúng tôi dùng ít lớp mặt nạ hơn.”

Tuy nhiên, EUV vẫn chưa được đưa vào sản xuất do một số khó khăn về nguồn sáng, chất cản quang, và việc sản xuất mặt nạ.

Hiện nay, ASML đang chuyển giao phiên bản mới nhất của loại máy quét EUV—mã số NXE:3350B. Thiết bị này sử dụng bước sóng 13.5nm và có độ mở là 0.33, độ phân giải half-pitch là 16nm.

ASML cũng nâng cấp nguồn của máy quét từ 80-watt lên 125-watt. Việc này sẽ tăng tốc độ xử lý từ 55-65 wafer một giờ lên 85 wafer một giờ. Thêm vào đó, ASML cũng đang sắp sửa cho ra một phiên bản nữa trong dòng máy quét EUV—chiếc NXE:3400B. Được dự định dùng cho cho công nghệ 5nm, NXE:3400B có độ phân giải 13nm.

Công ty cũng dự định sẽ ra mắt bộ nguồn công suất khoảng 200-watt (hay cao hơn nữa) trong năm nay hoặc năm sau. Nhưng cũng như trước kia, các nhà sản xuất chíp muốn có máy EUV với bộ nguồn 250-watt để dùng trong sản xuất với số lượng lớn. Bộ nguồn 250-watt sẽ cho phép xử lý 125 wafer mỗi giờ.

![]()

“Chúng tôi vẫn còn rất nhiều việc phải làm để tăng tốc độ khắc bằng EUV lên đến mức cần thiết,” theo Harry Levinson, thành viên cao cấp và là giám đốc cấp cao về nghiên cứu công nghệ ở GlobalFoundries.

Thêm vào đó, các nhà sản xuất còn gặp khó khăn trong việc tạo ra các chất cản EUV có thể hoạt động với các chi tiết có half-pitch nhỏ hơn 30nm. “Nếu chúng tôi có được độ nhạy cản quang vào mức 20 phần ngàn joule trên mỗi centimet vuông thì chúng tôi có thể đạt đến mức chi phí tương đương với kĩ thuật khắc immersion ba bước,” Levinson nói.

“Theo các số liệu mà chúng tôi có vào thời điểm này thì chúng tôi không nghĩ rằng chúng tôi sẽ chế tạo được các dây dẫn với các mặt bên đủ phẳng với loại chất cản quang có độ nhạy 20 phần ngàn joule trên mỗi centimet vuông. Nhưng với công nghệ 7nm thì độ nhạy 30 phần ngàn joule trên mỗi centimet vuông có lẽ là đủ. Cho dù vậy thì vẫn chưa đạt được mức chi phí tương đương với kĩ thuật khắc immersion ba bước. Nhưng với các ưu điểm khác của EUV, đặc biệt là thời gian chiếu, thì đây cũng có thể được xem là một con số hợp lý và cho thấy EUV có thể được dùng cho công nghệ 7nm,” ông nói.

Tạo nanowire

Bước kế tiếp có lẽ là bước khó nhất trong quá trình chế tạo transistor kiểu gate-all-around. Đó là bước tạo ra các nanowire.

Sau khi thực hiện các công đoạn khắc, cấu trúc sẽ có hình dạng chữ H. Như đã nói ở trên, hai vạch đứng là các cực source và drain. Phần gạch nối ở giữa là nơi các nanowire sẽ được hình thành.

Trong bước này, Imec và các công ty khác đã phát triển một phương pháp chế tạo cực cổng kim loại bằng cách thay thế. Ban đầu, phần ở giữa này là một siêu lớp bao gồm các lớp SiGe và silicon xen kẽ nhau.

Sử dụng một kĩ thuật thay thế, các lớp SiGe trong siêu lớp sẽ được gỡ bỏ. Còn lại sẽ là các lớp silicon với một khoảng trống giữa chúng. Về cơ bản, mỗi lớp silicon tạo thành một nanowire. Mỗi nanowire được kéo căng bởi SiGe để tăng khả năng dẫn của kênh truyền.

Trong trường hợp lý tưởng thì mỗi transistor sẽ có ba nanowire. Các nanowire sẽ chạy theo phương nằm ngang và được treo lơ lửng từ cực source sang cực drain.

Về cơ bản, ba nanowire sẽ nằm xếp chồng lên nhau (tầng trên cùng, tầng giữa, và tầng dưới cùng). Các nanowire được ngăn cách với nhau bởi một khoảng trống và chúng không tiếp xúc với nhau.

Thông thường, trong quy trình thay thế cực cổng này, các nhà sản xuất dùng kĩ thuật ăn mòn (etch) để loại bỏ các vật liệu. Nhưng các chất ăn mòn thông thường có thể không đáp ứng được yêu cầu về kích thước trong gate-all-around.

Điều khó khăn trong kĩ thuật này là ta phải loại bỏ được SiGe trong các cấu trúc có kích thước 15 ăng-strom hay nhỏ hơn. (1 ăng-strom bằng 0.1nm.) Không những thế SiGe phải được loại bỏ mà không làm ảnh hưởng tới các phần khác của transistor.

Trong quy trình này, các nhà sản xuất chíp dùng một công nghệ khắc thế hệ mới có tên gọi là khắc lớp nguyên tử (atomic layer etch, ALE). Công nghệ này có khả năng loại bỏ các vật liệu một cách có chọn lọc ở mức độ phân tử. Trên lý thuyết thì ALE có thể loại bỏ SiGe giữa các lớp silicon mà không gây hư hại hay để lại tàn dư gì.

“Ý tưởng là loại bỏ một cách có chọn lọc SiGe trong silicon,” theo Matt Cogorno, chịu trách nhiệm quản lý sản phẩm toàn cầu của Applied Materials. “Nhờ cách loại bỏ có chọn lọc này, ta tạo nên các nanowire.”

Tuy nhiên vẫn còn có một số trở ngại. “Có một kênh dẫn ký sinh được tạo ra bên dưới các nanowire. Ta phải tìm ra cách để loại bỏ sự rò rỉ qua kênh dẫn ký sinh đó,” Mocuta (Imec) nói. “Chúng tôi làm điều này bằng cách dùng một kĩ thuật mà chúng tôi gọi là “ground plane doping”. Chúng tôi thêm các vật liệu vào phần wafer bên dưới trước khi tạo siêu lớp. Điều này loại bỏ sự rò rỉ và cải thiện đặc tính dẫn điện của transistor.”

Transistor gate-all-around của Imec với hai nanowire nằm chồng lên nhau.

Cực gate và các dây dẫn kết nối

Bây giờ ta phải tạo cực gate cho transistor. Các vật liệu dùng để hình thành cực gate sẽ được đưa vào khoảng trống giữa cực source và cực drain bằng một kĩ thuật phủ vật liệu có tên gọi là atomic layer deposition (ALD, phủ từng lớp nguyên tử). Nhờ đó cực gate sẽ bọc quanh các nanowire.

“Kĩ thuật phủ vật liệu thực sự gặp khó khăn ở bước này,” Fried (Coventor) nói. “Trong một finFET, khi nhìn từ bên trên xuống ta thấy một cái rãnh được tạo ra bởi cực gate và cái fin sẽ nằm trong đó. Vật liệu sẽ được phủ lên trên toàn bộ bề mặt. Tất nhiên là sẽ có đôi chút khó khăn trong việc phủ lên hai bên vách của cái fin. Nhưng ta có thể thấy nơi mà ta muốn thêm vật liệu vào.”

Với gate-all-around thì đó lại là chuyện hoàn toàn khác. “Giờ đây, khi nhìn từ trên xuống, tôi chỉ thấy những sợi nanowire này. Tôi phải thêm vật liệu vào xung quanh chúng cả ở những chỗ mà tôi không nhìn thấy. Và tôi phải đảm bảo rằng vật liệu được phủ thật đều,” Fried nói.

Những người khác cũng đồng ý. “Ta không nhìn thấy một cách trực tiếp được. Ta không chỉ phải phủ lên bên trên nanowire mà ta còn phải phủ lên cả phần bên dưới của chúng. Ta cần phải có các phương pháp hoá học hoạt động một cách hoàn hảo,” theo Mohith Verghese, giám đốc tiếp thị sản phẩm toàn cầu của ASM International (ASMI).

Giải pháp? “Chúng ta sẽ thấy phương pháp ALD nhiệt quay trở lại. Đó sẽ là một giải pháp hoàn toàn dựa trên các hoá chất,” Verghese nói. Về cơ bản, ALD nhiệt là một quá trình hai giai đoạn và sử dụng hai chất phản ứng—A và B. Chất thứ nhất, A, được bơm vào ngăn phản ứng ALD. Wafer được xử lý rồi các hoá chất được xả ra. Sau đó, chất thứ hai, B, lại trải qua quá trình tương tự.

Mặc dù vậy, các dây dẫn kim loại mới có thể là trở ngại lớn nhất trong công nghệ 5nm. Để giải quyết vấn đề về độ trễ RC, các nhà sản xuất chíp cần có những bước đột phá. “Đó là một bài toán khó,” Hemker nói. “Ta sẽ phải tiếp cận vấn đề này từ mọi góc độ. Ta sẽ phải đưa ra được một giải pháp hoàn chỉnh về vật liệu, thiết bị, quy trình tích hợp, và thiết kế linh kiện.”

Thế hệ công nghệ tiếp theo

Trong nghiên cứu và phát triển, các công ty sản xuất chíp cũng đang tìm hiểu về công nghệ 3nm và xa hơn nữa, mặc dù chưa có gì rõ ràng là những công nghệ này có thể xảy ra hay không.

Với công nghệ 3nm, người ta đang tìm hiểu khả năng dùng các transistor gate-all-around theo phương ngang cũng như các transistor dùng nanowire theo phương thẳng đứng. “Chúng tôi cũng đang kết hợp với một số trường đại học để nghiên cứu về nanowire theo phương thẳng đứng. Nếu ta có thể chế tạo chúng và tạo được các kết nối với chúng thì sẽ rất tuyệt. Hiện nay khả năng hoạt động của transistor không còn tăng tương ứng với mật độ của chúng nữa. Khi ta liên tục thu nhỏ transistor thì mức độ rò rỉ sẽ tăng lên qua mỗi thế hệ công nghệ. Với cách mới này thì mức độ rò rỉ phụ thuộc vào chiều cao của sợi nanowire, còn mật độ thì lại phụ thuộc vào đường kính. Do vậy chúng tách bạch với nhau hơn. Tất nhiên ta vẫn phải tìm ra cách để tạo ra những cấu trúc này và sản xuất chúng. Còn rất nhiều việc phải làm,” Hemker nói.

Bên cạnh đó, complementary FET cũng đang được chú ý. Linh kiện này giống như một transistor gate-all-around: một nanowire tạo thành một nFET, còn sợi kế tiếp tạo thành một pFET, và cấu trúc đó được lặp đi lặp lại. “Ta chỉ việc tạo lớp cách điện giữa các linh kiện này rồi xếp chồng chúng lên nhau,” Fried nói. “Đó sẽ là một cuộc cách mạng. Nó sẽ thay đổi hoàn toàn cách thức làm tăng mật độ mạch điện. Và nó sẽ là một thử thách thực sự.”

Nguồn: Nguyên bản tiếng Anh: “What Transistors Will Look Like At 5nm,” Mark Lapedus, August 18, 2016

Người dịch: Tạ Minh Chiến

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn

Bạn Chưa Biết Phương Thức Nào Nhanh Chóng Để Đạt Được Chúng

Hãy Để Chúng Tôi Hỗ Trợ Cho Bạn. SEMICON

Hotline: 0972.800.931 - 0938.838.404 (Mr Long)