Nếu bạn đã làm quen với FPGA và HDL, hẳn bạn phải biết TestBench là gì. Tôi viết bài này là bài khởi đầu cho các bài nhằm mục đích cung cấp cho người mới bắt đầu một số kỹ năng viết testbench bằng VHDL, dựa trên kiến thức của cá nhận tôi.

Trước hết, bạn phải biết Test bench là gì?

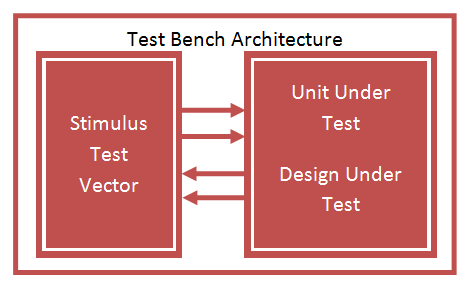

Một test bench là một môi trường ảo được sử dụng để kiểm chứng sự chính xác của việc thiết kế một mô hình.

Một file VHDL test bench là file hỗ trợ cho việc mô phỏng sự hoạt động của 1 entity cũng được viết bằng VHDL. Bằng cách mô tả thời gian, giá trị tín hiệu vào cho các chân input của entity cần kiểm chứng, test bench giúp người lập trình kiểm chứng được hoạt động của entity đó.

Về cơ bản, cấu trúc của 1 file VHDL test bench gồm 3 phần chính giống như khi tạo 1 entity thông thường trong VHDL

- Khai báo thư viện sử dụng

- Khai báo tên của entity test bench, thông thường tên của entity này có dạng [tên entity cần mô phỏng]_tb.vhd. Đây là 1 entity đặc biệt, không có input cũng như output.

- Khai báo kiến trúc của entity:

+ Khai báo component (entity cần mô phỏng)

+ Khai báo các chân trung gian (trùng tên với các inputs và outputs của entity cần mô phỏng)

+ Port map (nối các chân của entity cần mô phỏng với các chân trung gian ở trên)

+ Mô tả thời gian và giá trị của các tín hiệu vào

Ngoại trừ phần mô tả thời gian và giá trị của các tín hiệu vào, các phần khác gần như có khuôn mẫu sẵn và có nhưng chương trình hỗ trợ luôn việc sinh code đó. Xilinx cũng hộ trợ việc này. Tuy nhiên, chương trình này khá nặng và chỉ phù hợp với những người làm Xilinx, các bạn có thể vào đường link sau:

http://www.doulos.com/knowhow/perl/testbench_creation/

Paste đoạn code trong file chứa entity cần mô phòng vào, ấn nút “Generate VHDL test bench”, chương trình sẽ tự động sinh code và bạn chỉ cần viết phần quan trọng nhất tôi đã nói ở trên.

Để minh hoạt cho ví dụ này, tôi sử dụng entity của Lab1 part 1 trong bộ 10 bài Lab của Altera về VHDL cho Kit DE1.

Sau khi sinh ra đoạn code test bench, viết thêm đoạn code sau vào phần “stimulus: process”

Sau khi mô phỏng bằng ModelSim, chúng ta có được waveform như sau:

Trong phần mô phỏng này, ta nhận thấy giá trị của LED lúc nào cũng bằng giá trị của SW, vậy ta đã viết code đúng.

Vậy là ta đã có một cách viết testbench khá đơn giản.

Đối với bạn mới học VHDL, bạn nên đọc để hiểu các lệnh “wait”, “wait for” (Trong tài liệu MIT Press Circuit Design with VHDL viết khá cụ thể)

Nguồn: esrc618

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn

Bạn Chưa Biết Phương Thức Nào Nhanh Chóng Để Đạt Được Chúng

Hãy Để Chúng Tôi Hỗ Trợ Cho Bạn. SEMICON

Hotline: 0972.800.931 - 0938.838.404 (Mr Long)