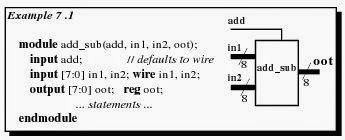

Cấu trúc module Verilog

Friday, 05 April 2019 20:35

Semicon Editor 01

1. Giới thiệu Khác với các ngôn ngữ lập trình C,C++… Verilog được cấu trúc từ các module giống như một chương trình chính (chương trình main) trong C,C++….một module tương đương với 1 block (1 khối chức năng) trong thiết kế. Giống như C, từ hàm main ta có thể tạo ra nhiều hàm con khác thì Verilog cũng vậy, một module chính (top module) có thể được tạo từ các module con khác.

Last Updated ( Friday, 05 April 2019 20:44 )

Read more...

Dataflow - mô hình luồng dữ liệu trong verilog.

Friday, 05 April 2019 20:19

Semicon Editor 01

1. Giới thiệu: - Đối với các thiết kế nhỏ, các phương pháp mô hình gate-level (mức cổng) làm việc rất tốt vì số lượng các cổng là hạn chế. Chúng ta có thể thiết kế nhanh chóng và kết nối mỗi cổng riêng biệt lại với nhau dễ dàng.

Last Updated ( Friday, 05 April 2019 20:36 )

Read more...

Mỗi con chip có hàng tỷ bóng bán dẫn, chuyện gì sẽ xảy ra nếu một vài bóng bán dẫn trong đó bị hỏng?

Thursday, 04 April 2019 19:38

Semicon Editor 01

Về cơ bản, số lượng bóng bán dẫn* sẽ tỉ lệ thuận với hiệu năng CPU và tỉ lệ nghịch với mức tiêu thụ điện năng, tức càng nhiều bóng bán dẫn trên 1 diện tích, hiệu năng càng tăng nhưng mức điện tiêu hao cũng ít đi. Nhưng điều gì sẽ xảy ra nếu một vài trong hàng tỉ bóng bán dẫn có trên CPU bị hỏng?

Read more...

Để giữ Định luật Moore sống mãi, đã đến lúc chúng ta cần đến giải pháp ánh sáng

Wednesday, 03 April 2019 19:22

Semicon Editor 01

Kích thước của chip bán dẫn đã tới gần giới hạn của sản xuất và tốc độ, liệu định luật Moore đã đến hồi kết hay vẫn còn một giải pháp khả thi khác.

Read more...

Vì sao bóng bán dẫn nghe mong manh như thế nhưng chúng hầu như không bao giờ hỏng?

Wednesday, 03 April 2019 19:14

Semicon Editor 01

Với số lượng bóng bán dẫn cực nhiều như thế, tại sao chúng ta rất hiếm khi nghe thấy trường hợp bể bóng bán dẫn, hay chip xử lí đã bị hư hại các bóng bán dẫn bên trong, mặc dù cái tên bóng bán dẫn nghe khá là... mong manh?

Last Updated ( Wednesday, 03 April 2019 19:19 )

Read more...

Tổng quan về phân tích Timing tĩnh

Tuesday, 02 April 2019 18:52

Semicon Editor 01

Timing (định thời) là những quy định về mặt thời gian mà các mạch số cần phải tuân thủ và đáp ứng khi được tổng hợp và layout. Timing là một trong các yếu tố quan trọng luôn phải được xem xét, đánh giá khi tổng hợp, layout mạch số.

Last Updated ( Tuesday, 02 April 2019 19:00 )

Read more...

Tổng quan về Timing Analysis trong ASIC

Tuesday, 02 April 2019 18:35

Semicon Editor 01

1. Timing là gì? Timing đơn giản là thời gian, là đáp ứng về mặt thời gian của cell logic - cell delay, của dây nối (net/wire) - net delay, của các hiện tượng điện tử trong mạch có thể gây ra delay, ảnh hưởng đến hoạt động của thiết kế.

Last Updated ( Wednesday, 03 April 2019 18:14 )

Read more...

Bóng bán dẫn mới giúp thiết bị hoạt động lâu mà không cần sạc

Monday, 01 April 2019 20:23

Semicon Editor 01

Các kỹ sư từ Đại học Cambridge đã tạo ra một bóng bán dẫn sử dụng năng lượng cực thấp, khiến nó có thể hoạt động trong thời gian dài mà không cần sạc điện. Công nghệ mới này có thể được sử dụng trong các cảm biến và nhiều thiết bị khác nhau, giúp chúng có thể tự sử dụng nguồn năng lượng lâu bền này.

Last Updated ( Monday, 01 April 2019 20:26 )

Read more...

Phân biệt vi điều khiển - CPLD - FPGA

Sunday, 31 March 2019 18:55

Semicon Editor 01

1.FPGA là gì?

Last Updated ( Sunday, 31 March 2019 19:05 )

Read more...

Tổng quan về Verilog HDL

Friday, 29 March 2019 20:47

Semicon Editor 01

1. Verilog HDL là gì?

Last Updated ( Thursday, 11 April 2019 19:23 )

Read more...

Shell là gì? Phân loại và ứng dụng trong ngành vi mạch

Friday, 29 March 2019 19:39

Semicon Editor 01

1.Shell là gì?

Last Updated ( Wednesday, 26 June 2019 18:37 )

Read more...

Sơ lược về độ trể (Delay) trong thiết kế ASIC

Thursday, 28 March 2019 18:29

Semicon Editor 01

Về cơ bản nhất, delay có thể được chia thành 2 loại:

Last Updated ( Thursday, 28 March 2019 18:34 )

Read more...

Thiết kế FPGA

Tuesday, 26 March 2019 18:51

Semicon Editor 01

Chia làm 2 phương pháp:

Last Updated ( Tuesday, 26 March 2019 19:01 )

Read more...

Các bài thí nghiệm cơ bản trên FPGA

Tuesday, 26 March 2019 18:37

Semicon Editor 01

Các bài thí nghiệm cơ bản theo tiêu chuẩn của Altera bao gồm hai hệ thống bài tập thí nghiệm về hệ thống số và cấu trúc máy tính. các bài thí nghiệm được biên soạn cho kít thí nghiệm FPGA DE2.

Last Updated ( Tuesday, 26 March 2019 18:40 )

Read more...

FPGA làm việc như thế nào?

Tuesday, 26 March 2019 18:18

Semicon Editor 01

1. Cấu trúc cơ bản của FPGA

Last Updated ( Tuesday, 26 March 2019 18:26 )

Read more...

|

|