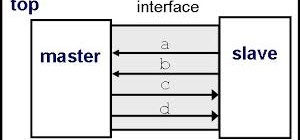

Một trong những tính năng hay nhất mà SystemVerilog hỗ trợ là từ khóa interface. Các kĩ sư thiết kế không còn phải tốn thời gian để lặp đi lặp lại công việc nối dây (wire connectivity) giữa module với module, hay module với testbench.

Một trong những tính năng hay nhất mà SystemVerilog hỗ trợ là từ khóa interface. Các kĩ sư thiết kế không còn phải tốn thời gian để lặp đi lặp lại công việc nối dây (wire connectivity) giữa module với module, hay module với testbench.

Interface sẽ giúp công việc này được thực hiện một cách nhanh chóng và dễ dàng. Đồng thời, hạn chế bug xảy ra như kiểu nối dây cũ mà Verilog hỗ trợ.

Về cơ bản, interface hỗ trợ việc nhóm (grouping) các nhiều tín hiệu lại thành một tín hiệu, làm giảm độ phức tạp khi handle các tín hiệu này, đồng thời giúp cho việc coding dễ dàng. Interface có thể bao gồm cả task, function, parameter, …

Ví dụ đơn giản về cách khai báo và sử dụng interface như sau:

// Interface definition

interface Bus;

logic [7:0] Addr, Data;

logic RWn;

endinterface

// Using the interface

module TestRAM;

Bus TheBus(); // Instance the interface

logic[7:0] mem[0:7];

RAM TheRAM (.MemBus(TheBus)); // Connect it

initial

begin

TheBus.RWn = 0; // Drive and monitor the bus

TheBus.Addr = 0;

for (int I=0; I<7; I++)

TheBus.Addr = TheBus.Addr + 1;

TheBus.RWn = 1;

TheBus.Data = mem[0];

end

endmodule

module RAM (Bus MemBus);

logic [7:0] mem[0:255];

always @*

if (MemBus.RWn)

MemBus.Data = mem[MemBus.Addr];

else

mem[MemBus.Addr] = MemBus.Data;

endmodule

Ở đây chúng ta có thể thấy, việc kết nối giữa testbench và DUT chỉ được thực hiện một cách rất đơn giản bằng 1 dòng code.

RAM TheRAM (.MemBus(TheBus)); // Connect it.