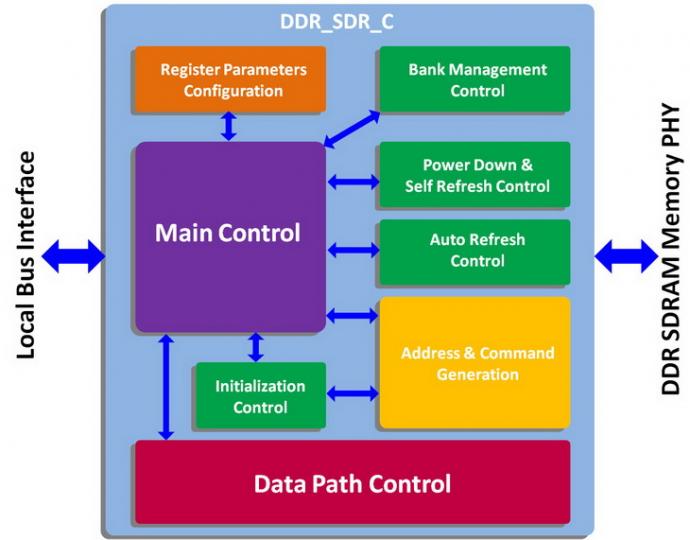

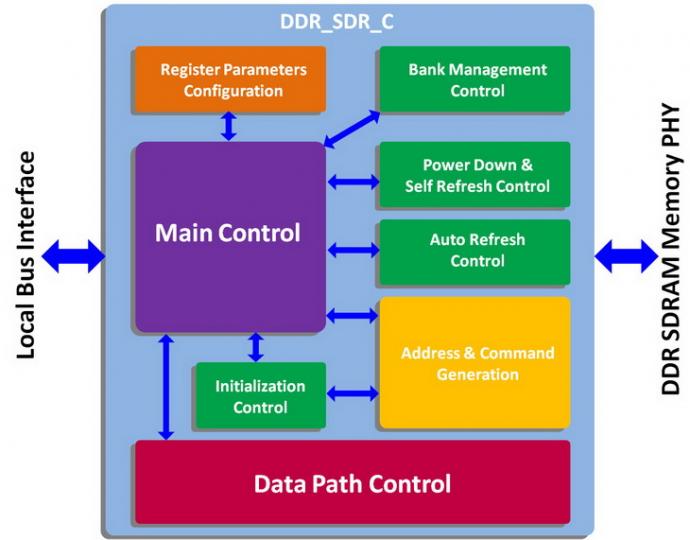

DDR_SDR_C hoạt động với hiệu suất cao giao tiếp với các thiết bị bộ nhớ DDR SDRAM. Bus giao tiếp cục bộ truyền các lệnh đọc và ghi đến bộ điều khiển. Sau khi DDR_SDR_C nhận được các lệnh này và chuyển chúng thành chuỗi lệnh trình tự theo yêu cầu của thiết bị DDR SDRAM. DDR_SDR_C cũng thực hiện chức năng khởi tạo ban đầu, tự động làm tươi, và power-down, self-refresh cho thiết bị bộ nhớ.

DDR_SDR_C cũng sử dụng kỹ thuật quản lý băng để theo dõi trạng thái của bốn băng DDR SDRAM. Các băng chỉ được mở hoặc đóng khi nó cần thiết để giảm độ trễ truy cập.

Đặc điểm chính

- Giao tiếp theo chuẩn công nghiệp DDR SDRAM

- Có thể lập trình burst length với 2, 4 hoặc 8

- Có thể lập trình độ trễ chu kỳ CAS với 2, 2.5 hoặc 3

- Có thể cấu hình run-time các thông số định thời (tRAS, tRC, tRFC, tRP, tMRD, tREFC, tWR, CAS Latency)

- Có thể cấu hình run-time số bit hàng và cột

- Trình quản lý theo dõi trạng thái của mỗi bank DDR SDRAM, hỗ trợ đến băng

- Tự động tạo khởi tạo ban đầu và làm tươi cho thiết bị bộ nhớ

- Hỗ trợ lệnh tự động precharge để tối ưu hiệu suất của sự truy xuất thiết bị với địa chỉ ngẫu nhiên

- Hỗ trợ chế độ tiết kiệm năng lượng (power-down và self-refresh)

- Hỗ trợ giao tiếp với tối đa 8 chip, mỗi chip tối đa 1GBbit

- Hỗ trợ nhiều loại thiết bị DDR SDRAM và DIMM.

Tần số và tài nguyên

| Tần số | Tài nguyên |

| Stratix II | 200 MHz | 570 ALUTs |

Mã nguồn và tài liệu

- Mã nguồn RTL (Verilog HDL)

- Mã nguồn kiểm tra (Verilog HDL)

- Tài liệu

(Theo icdrec)