Introduction

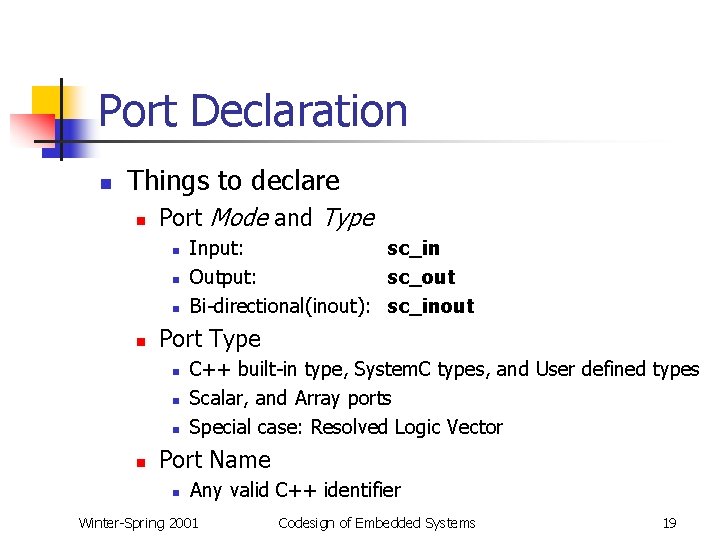

In this chapter we shall see ports and signal types in details.

Accessing Ports/Signals

In last chapter we saw how ports are declared and different types of ports. Here we will see how to access them. It is not a good idea to access ports directly, either for reading or writing. Port data types should use following methods to access them.

- port_name.write('value') : For writing value to port

- port_name.read() : For reading value from port

write() and read() methods does the automatic type conversion from other data types to port data types. It is not always possible to use same data types of ports or signals inside processes. When using different data types, it is always good to use port_name.read() and port_name.write("value") to access the ports and same rule apply for signals.

Example : Accessing Ports/Signals

1 #include

2

3 SC_MODULE(ports_access) {

4 sc_in<sc_bit> a;

5 sc_in<sc_bit> b;

6 sc_in<bool> en;

7 sc_out<sc_lv<2> > out;

8

9 // Method to manipulate output

10 void body () {

11 // Ports should use read() method to read values

12 if (en.read() == 1) {

13 // Should use write() method of write values

14 out.write(a.read() + b.read());

15 }

16 }

17 // Method to monitor ports

18 void monitor () {

19 cout << "@" << sc_time_stamp() <<" a : " << a

20 << " b : " << b << " en : " << " out : "

21 << out.read() <<endl;

22 }

23

24 SC_CTOR(ports_access) {

25 SC_METHOD(body);

26 sensitive << a << b << en;

27 SC_METHOD(monitor);

28 sensitive << a << b << en << out;

29 }

30

31 };

32

33 // Testbench to generate test vectors

34 int sc_main (int argc, char* argv[]) {

35 sc_signal <sc_bit> a;

36 sc_signal <sc_bit> b;

37 sc_signal <bool> en;

38 sc_signal <sc_lv<2> > out;

39

40 ports_access prt_ac("PORT_ACCESS");

41 prt_ac.a(a);

42 prt_ac.b(b);

43 prt_ac.en(en);

44 prt_ac.out(out);

45

46 sc_start(0);

47 // Open VCD file

48 sc_trace_file *wf = sc_create_vcd_trace_file("ports_access");

49 sc_trace(wf, a, "a");

50 sc_trace(wf, b, "b");

51 sc_trace(wf, en, "en");

52 sc_trace(wf, out, "out");

53 // Start the testing here

54 sc_start(1);

55 a = sc_bit('0');

56 b = sc_bit('0');

57 en = 1;

58 sc_start(1);

59 a = sc_bit('1');

60 sc_start(1);

61 b = sc_bit('1');

62 sc_start(2);

63

64 sc_close_vcd_trace_file(wf);

65 return 0;// Terminate simulation

66 }

Simulation Output: Accessing Ports/Signals

SystemC 2.0.1 --- Oct 6 2006 19:17:37

Copyright (c) 1996-2002 by all Contributors

ALL RIGHTS RESERVED

@0 s a : 0 b : 0 en : out : XX

WARNING: Default time step is used for VCD tracing.

@1 ns a : 0 b : 0 en : out : XX

@1 ns a : 0 b : 0 en : out : 00

@2 ns a : 1 b : 0 en : out : 00

@2 ns a : 1 b : 0 en : out : 01

@3 ns a : 1 b : 1 en : out : 01

@3 ns a : 1 b : 1 en : out : 10

Bạn Có Đam Mê Với Vi Mạch hay Nhúng - Bạn Muốn Trau Dồi Thêm Kĩ Năng

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn